Mielőtt belekezdünk ebbe a cseppet sem könnyű témába, melyben megnézzük a félvezető-technológia jelenleg ismert határait, érdemes lesz kitölteni azt a csésze kávét. Ha megvagy, akkor csapjunk bele, mert érdekes!

A miniatürizálástól az Angström-korszakig és a poszt-szilícium világáig

A modern civilizáció technológiai alapjait az elmúlt hat évtizedben egyetlen empirikus megfigyelés, a Moore-törvény vezérelte.

Gordon Moore, az Intel társalapítója 1965-ben vázolta fel azt a jövőképet, amely szerint az integrált áramkörökön elhelyezett tranzisztorok száma kétévente megduplázódik, miközben az egységnyi tranzisztorra jutó költség minimalizálódik. Ez a tendencia tette lehetővé a számítástechnikai teljesítmény exponenciális növekedését, a szuperszámítógépektől kezdve a zsebünkben hordott okostelefonokig.

Azonban a 2020-as évek közepére az iparág elérte azt a kritikus pontot, ahol a puszta méretcsökkentés már nem csupán mérnöki kihívás, hanem fundamentális fizikai korlátokba ütközik. Ahogy a tranzisztorok kritikus méretei az atomi skála közelébe kerülnek, a klasszikus fizika szabályait felváltják a kvantummechanika kiszámíthatatlan jelenségei, kényszerítve a kutatókat és mérnököket, hogy alapjaiban gondolják újra a félvezetők architektúráját, anyagtudományát és rendszerszintű integrációját.

A Moore-törvény evolúciója és a skálázás válsága

A Moore-törvény soha nem volt természeti törvény a szó fizikai értelmében; sokkal inkább egy gazdasági és technológiai útitervként szolgált a félvezetőipar számára. Az 1970-es években a tranzisztorok mérete még mikrométeres nagyságrendű volt, ám 2024-re a legfejlettebb chipek már a 2 nanométeres skálán készülnek, ami ötezerszeres csökkenést jelent.

Ez a folyamat azonban drasztikusan lelassult. Míg korábban a tranzisztorsűrűség duplázódása szigorúan követte a 24 hónapos ciklust, ma ez az időszak inkább a három-négy évhez közelít.

A miniatürizálás lelassulásának hátterében három fő akadály áll: a kvantummechanikai korlátok, a hőkezelési nehézségek és a gyártási költségek robbanásszerű növekedése. A tranzisztorok sűrűségének növekedésével az egységnyi területen keletkező hő olyan mértékű, hogy a hagyományos hűtési módszerek már nem elegendőek, ami a teljesítmény korlátozásához vezet.

Gazdasági szempontból egy modern, 2 nanométer alatti csomópontot használó gyár (fab) felépítése több tízmilliárd dollárt igényel, és az extrém ultraibolya (EUV) litográfiai gépek darabja meghaladja a 150-350 millió dollárt.

| Technológiai korszak | Jellemző csomópont | Tranzisztorok száma (lapka szintjén) | Kulcsfontosságú innováció |

| 1970-es évek | 10 \mu m | ~2,300 | Planar MOSFET |

| 2010-es évek | 22 nm – 14 nm | ~1 – 5 milliárd | FinFET architektúra |

| 2020-as évek | 5 nm – 3 nm | ~50 – 100 milliárd | EUV litográfia |

| 2025 után | 2 nm – 18A | > 100 milliárd | GAAFET és Hátoldali tápellátás |

A kvantummechanikai fal: Alagúteffektus és bizonytalanság

Amikor a tranzisztor szigetelőrétegei és csatornái elérik a néhány nanométeres vastagságot, az elektronok már nem viselkednek klasszikus részecskékként. A kvantummechanikai alagutazás (quantum tunneling) jelensége lehetővé teszi, hogy az elektronok áthaladjanak (vagy „átteleportálódjanak”) olyan energiagátakon, amelyeket a klasszikus fizika szerint nem tudnának leküzdeni.

A kvantumalagutazás fizikája

A kvantummechanikai modellben a részecskéket hullámfüggvényekkel írjuk le. Ha egy elektron egy vékony szigetelőréteghez (potenciálgáthoz) ér, a hullámfüggvénye nem szakad meg hirtelen, hanem exponenciálisan gyengülve behatol a gátba. Ha a gát elég vékony – tipikusan 1-2 nanométer alatti –, a hullámfüggvény értéke a gát túloldalán nem nulla, ami azt jelenti, hogy fennáll egy jól meghatározható valószínűsége annak, hogy az elektron a szigetelő túloldalán jelenik meg.

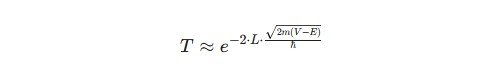

A transzmissziós valószínűség (T) matematikai közelítése vékony téglalap alakú gát esetén:

Ahol:

-

L a gát szélessége (nanométerben).

-

m az elektron tömege.

-

V a potenciálgát magassága.

-

E az elektron kinetikus energiája.

-

\hbar a redukált Planck-állandó.

Ebből látható, hogy a gát szélességének (L) kismértékű csökkenése az alagutazási valószínűség (és így a szivárgási áram) exponenciális növekedését eredményezi. Ez az irányíthatatlan áramszivárgás teszi használhatatlanná a hagyományos szilícium tranzisztorokat a 2 nanométer alatti tartományban, mivel a tranzisztor „kikapcsolt” állapotában is jelentős mennyiségű áram folyik keresztül, ami adatvesztéshez és extrém melegedéshez vezet.

A Heisenberg-féle határozatlansági elv hatása

A méretcsökkentés másik korlátja a Heisenberg-féle határozatlansági elv, amely kimondja, hogy egy részecske helyét (\Delta x) és impulzusát (\Delta p) nem lehet egyszerre tetszőleges pontossággal meghatározni:

Ahogy a tranzisztor mérete (\Delta x) csökken, az elektron impulzusának (és így energiájának) bizonytalansága megnő. Ez instabilitást okoz a tranzisztor kapcsolási állapotában, bizonytalanná téve, hogy az adott pillanatban 0 vagy 1 állapotban van-e az eszköz. Az iparág jelenleg azon a határon egyensúlyoz, ahol a megbízhatóság fenntartása már nem oldható meg a hagyományos szilícium-alapú síkbeli struktúrákkal.

Új architektúrák: A 3D kialakítás diadala

A kvantummechanikai kihívásokra a mérnökök a tranzisztor térbeli szerkezetének megváltoztatásával válaszoltak. A cél az elektrosztatikus kontroll javítása a csatorna felett, hogy megakadályozzák az elektronok szökését.

A FinFET-től a GAAFET-ig

A 2010-es évek elején a síkbeli (planar) tranzisztorokat felváltotta a FinFET (Fin Field-Effect Transistor) architektúra. Itt a csatorna egy függőleges „uszonyként” emelkedik ki, amelyet a kapu (gate) három oldalról vesz körül. Ez jelentős előrelépést jelentett, de a 3 nanométer alatti skálázásnál már a FinFET is eléri határait, mivel az uszony alján továbbra is felléphet szivárgás.

A megoldást a Gate-All-Around (GAAFET), vagy más néven nanosheet tranzisztor jelenti. Ebben a struktúrában a csatorna nem egy uszony, hanem több, egymás fölé rakott vízszintes szalag (nanosheet), amelyeket a kapu minden oldalról – 360 fokban – körülölel. Ez a kialakítás biztosítja a maximális elektrosztatikus kontrollt, hatékonyan elfojtva a rövidcsatorna-hatásokat és minimalizálva a kvantumalagutazásból eredő szivárgást.

| Tranzisztor típus | Kapu vezérlés | Skálázhatósági határ | Előnyök |

| Planar MOSFET | 1 oldalról | ~20 nm | Egyszerű gyártás |

| FinFET | 3 oldalról | ~5-3 nm | Jó áramvezérlés |

| GAAFET (Nanosheet) | Minden oldalról | ~1 nm | Kiváló kontroll, alacsony szivárgás |

| CFET (Complementary FET) | Vertikális stack | < 1 nm | Maximális sűrűség |

A CFET és a jövőbeli struktúrák

A GAA-korszak után az imec és a vezető gyártók útitervében a CFET (Complementary FET) szerepel. A CFET-nél az n-típusú és p-típusú tranzisztorokat nem egymás mellé, hanem közvetlenül egymás tetejére helyezik. Ez drasztikusan, akár 40-50%-kal csökkentheti a logikai cellák alapterületét anélkül, hogy magát a tranzisztort tovább kellene kicsinyíteni az atomi határ alá. A CFET tömeggyártása az A7 (0,7 nm) csomópont környékén a 2030-as évek elején várható.

Az Angström-korszak és a hátoldali tápellátás

Ahogy belépünk az Angström-korszakba (ahol a méreteket már nem nanométerben, hanem a tízszer kisebb Angströmben mérjük, pl. 18A = 1,8 nm), az egyik legnagyobb akadály már nem maga a tranzisztor, hanem a huzalozás. A modern chipeknél a tranzisztorok felett akár 15-20 rétegnyi fémezés található, amelyen a tápellátás és a jelek osztoznak. Ez a „huzalozási fal” (wiring wall) jelentős feszültségesést és jelkésleltetést okoz.

PowerVia és Super Power Rail

A megoldás a hátoldali tápellátási hálózat (BSPDN – Backside Power Delivery Network). Az Intel PowerVia és a TSMC Super Power Rail technológiája a tápellátást szolgáló vezetékeket a szilícium lapka hátoldalára helyezi át.

-

Hatékonyság: Ezáltal megszüntethető az „IR-drop” (feszültségesés), mivel a tápvezetékek közvetlenül csatlakoznak a tranzisztorok forrásához és nyelőjéhez.

-

Sűrűség: A tápvezetékek eltávolítása az elülső oldalról kb. 20%-kal több helyet szabadít fel a jelvezetékek számára, ami lehetővé teszi a tranzisztorsűrűség további növelését a tranzisztor fizikai méretének változtatása nélkül.

-

Teljesítmény: A TSMC A16 csomópontja a hátoldali tápellátásnak köszönhetően 15-20%-os fogyasztáscsökkenést ígér azonos sebesség mellett a 2 nm-es technológiához képest.

Anyagtudományi forradalom: A szilíciumon túl

Bár a szilícium dominanciája még kitart, a fizikai határok elérése kényszeríti az iparágat az alternatív anyagok kutatására. A szilícium mobilitása (az elektronok sebessége az anyagban) korlátozott, és vékony rétegekben az atomi érdesség jelentősen rontja a teljesítményt.

Szén nanocsövek (CNT) és grafén

A szén nanocsövek (CNT) lényegében hengerré csavart grafénlapok, amelyek átmérője mindössze 1 nanométer. A CNT-alapú tranzisztorok (CNFET) elméletileg ötször-tízszer energiahatékonyabbak lehetnek a szilíciumnál.

-

Ballisztikus vezetés: A CNT-ben az elektronok szinte ütközésmentesen, ballisztikusan haladhatnak, ami drasztikusan csökkenti a hőtermelést.

-

3D integráció: Mivel a CNFET-ek alacsony hőmérsékleten (400 °C alatt) gyárthatók, lehetővé teszik a logikai rétegek közvetlen egymásra építését, létrehozva valódi 3D-s mikroprocesszorokat. A fő kihívás jelenleg a „tisztaság” és az „orientáció”: milliárdnyi 1 nanométeres csövet kellene tökéletes rendben elhelyezni, ami olyan, mintha az egész Dunántúl nagy részét száraz spagettivel akarnánk lefedni tökéletesen párhuzamosan.

2D-s félvezetők (TMD-k)

A kétdimenziós anyagok, mint a molibdén-diszulfid (MoS_2) vagy a volfrám-diszelenid (WSe_2), egyetlen atomvastagságú rétegekből állnak. Ezek a transition metal dichalcogenide-ok (TMD) azért ígéretesek, mert még egyetlen atomi rétegben is megőrzik kiváló félvezető tulajdonságaikat, és nincs rajtuk „szabad kötés” (dangling bond), ami a szilíciumnál szóródást és szivárgást okoz a felületen. A TMD-alapú tranzisztoroknál már demonstrálták a 0,34 nanométeres kapuhosszat, ami a szilíciummal elképzelhetetlen.

| Anyag jellemzői | Szilícium (Bulk) | Szén nanocső (1D) | MoS2 (2D) |

| Elektron mobilitás (cm^2/Vs) | ~1,400 | ~3,000 – 100,000 | ~200 – 1,000 |

| Atomi vastagság | Nincs (3 nm alatt instabil) | 1 nm átmérő | 0.65 nm réteg |

| Gyárthatóság | Kiváló | Nehéz (rendezettség) | Közepes (növesztés) |

Rendszerszintű innováció: Chipletek és 3D IC

Mivel az egyes tranzisztorok zsugorítása már nem hoz automatikus költségcsökkenést, a hangsúly a chipek összeszerelésére terelődött. Ez a „More than Moore” stratégia, amely a rendszerszintű integrációt helyezi előtérbe.

A Chiplet-forradalom

A hagyományos monolitikus chipek (ahol minden funkció egyetlen nagy szilíciumdarabon van) helyett a chiplet architektúra kisebb, specializált egységeket használ.

-

Hozamjavítás: Egy nagy chipen egyetlen hiba az egész eszközt tönkreteheti. Kisebb chipleteknél a hiba esélye kisebb, így a gyártási hozam (yield) drasztikusan javul.

-

Heterogén integráció: Lehetővé teszi, hogy a nagy teljesítményű processzormagok a legdrágább 2 nm-es eljárással készüljenek, míg a memória-vezérlők vagy az I/O egységek olcsóbb, kiforrottabb technológiával. Az olyan szabványok, mint az UCIe (Universal Chiplet Interconnect Express), biztosítják, hogy a különböző gyártók chipletjei kompatibilisek legyenek egymással.

3D V-Cache és függőleges rétegezés

Az AMD 3D V-Cache technológiája egy kiváló példa a vertikális skálázásra. Itt az L3 gyorsítótárat közvetlenül a processzormagok tetejére (vagy az újabb generációknál alájuk) rétegezik.

-

Késleltetés: A memória fizikai közelsége drasztikusan csökkenti a késleltetést (latency), ami a játékoknál és az MI-számításoknál akár 15-25%-os teljesítménynövekedést hoz.

-

Hűtés: A 2. generációs 3D V-Cache-nél a gyorsítótár a magok alá került, így a processzormagok közvetlen kapcsolatban maradnak a hűtőbordával, ami magasabb órajelet tesz lehetővé.

Gazdasági realitások és a félvezető-geopolitika

A miniatürizálás határának elérése nemcsak tudományos, hanem hatalmas gazdasági kihívás is. A technológiai fejlődés fenntartása ma már csak a globális óriáscégek és államok szoros együttműködésével lehetséges.

Az 1 billió dolláros piac felé

A félvezetőipar bevételei 2030-ra várhatóan elérik az 1 billió (1000 milliárd) dollárt. Ez a növekedés hajtja a „CAPEX-háborút”: a TSMC 2026-os költségvetése elérheti az 56 milliárd dollárt, amit új gyárak építésére fordítanak Arizonában és Tajvanon. A szilícium mára fontosabb erőforrássá vált, mint az olaj; a technológiai szuverenitás alapköve, hogy egy ország képes-e biztosítani saját chipellátását.

A fejlődés fenntarthatósága

A Moore-törvény lelassulása kényszerű szemléletváltást hozott. A hangsúly a puszta sebességről az energiahatékonyságra és a fenntarthatóságra helyeződött. Az Nvidia legújabb Blackwell GPU-ja például ötször gyorsabb elődjénél, de 70%-kal több energiát fogyaszt, ami kifinomult folyadékhűtési megoldásokat igényel. A jövőben a „teljesítmény per watt” válik a legfontosabb mérőszámmá.

Alternatív számítási paradigmák

Amikor a tranzisztorok kicsinyítése végleg megáll, a fejlődésnek új utakat kell találnia. A kutatás már most folyik a nem-von-Neumann architektúrák irányába.

Neuromorf és kvantumszámítástechnika

A neuromorf számítástechnika az emberi agy működését utánozza: a chipek „neuronokból” és „szinapszisokból” állnak, amelyek csak akkor fogyasztanak energiát, ha tüzelnek. Ez nagyságrendekkel hatékonyabb lehet a hagyományos bináris logikánál az MI-feladatokban.

A kvantumszámítástechnika pedig nem a tranzisztorok számának növelésével, hanem a kvantumbitek (qubitek) szuperpozíciójának és összefonódásának kihasználásával old meg olyan problémákat, amelyek a klasszikus gépeknek évezredekbe telnének. Ironikus módon, míg a kvantumjelenségek (mint az alagutazás) akadályozzák a hagyományos chipek működését, a kvantumszámítógépekben éppen ezekre a jelenségekre építünk.

Kikövetkeztethető, hogy a félvezetőipar elérte azt a pontot, ahol a miniatürizálás már nem csupán mérnöki feladat, hanem a természet alapvető törvényeivel való küzdelem. A kvantummechanikai alagutazás és a hőkezelési korlátok véget vetettek a klasszikus skálázás korszakának, de nem vetettek véget a technológiai fejlődésnek.

Az elemzés alapján az alábbi fő következtetések vonhatók le:

-

Strukturális váltás: A tranzisztorok architektúrája végleg 3D-ssé vált. A GAAFET és a jövőbeli CFET struktúrák biztosítják az elektrosztatikus kontrollt, amely nélkül a tranzisztorok a szivárgási áramok miatt működésképtelenek lennének 3 nm alatt.

-

Vertikális skálázás: A jövő nem a vízszintes méretcsökkentésben, hanem a vertikális rétegezésben rejlik. A hátoldali tápellátás (BSPDN) és a 3D-s chipstacking lehetővé teszi a sűrűség növelését akkor is, ha az atomi méretek gátat szabnak a további kicsinyítésnek.

-

Anyagváltás kényszere: A szilíciumot hamarosan felválthatják a szén nanocsövek vagy a 2D-s TMD anyagok, amelyek atomi vastagságban is stabilabbak és jobb vezetőképességűek.

-

Rendszerszintű megközelítés: A Moore-törvényt már nem a tranzisztorszám, hanem a rendszerszintű hatékonyság (chipletek, szoftver-hardver ko-design) tartja életben.

A kérdésre, hogy „meddig miniatürizálhatunk?”, a válasz ma már nem egy nanométerben kifejezett szám, hanem az a képességünk, hogy mennyire tudjuk uralni az anyag elemi szintjén jelentkező kvantumjelenségeket. A miniatürizálás fizikai határa az atom, de a számítási teljesítmény határait az emberi innováció továbbra is tágítja.